Electronique

> Bases

> Compatibilité TTL / CMOS

Dernière mise à jour : 11/09/2011Présentation

Association dans un même montage électronique de circuits intégrés logiques TTL et CMOS : pas de soucis à se faire ou précautions à prendre ? On vient de me poser la question et oups... que dire... Oui, j'ai déjà réalisé quelques montages qui combinaient les deux technologies TTL et CMOS, mais de là à certifier 100% que ça marche à tous les coups... Une seule solution, ressortir les bouquins, faire quelques tests et ne pas oublier le résumé.Petits rappels

Avant de voir si on peut relier une sortie TTL sur une entrée CMOS ou une sortie CMOS sur une entrée TTL, il est sans doute utile de rappeler quelques notions de base.Sortance

La sortance s'exprime par un nombre entier et représente la capacité que possède la sortie d'un circuit à piloter en même temps plusieurs entrées de circuits de même type. Par exemple, une porte logique dont la sortance est 10 indique que cette sortie peut être raccordée en même temps sur 10 entrées différentes d'autres circuits logiques. Attention, ce chiffre n'indique nullement une capacité exprimée en courant (A) ou en puissance (W). Le courant maximal que peut fournir un circuit logique CMOS dont la sortance est de 50, peut être inférieur au courant maximal que peut délivrer la sortie d'une porte logique TTL dont la sortance est 10. La sortance est liée d'une part à la capacité en courant de sortie d'une porte, et est liée d'autre part à l'impédance d'entrée de la porte qui suit. Ainsi un circuit TTL de la famille LS qui présente une impédance d'entrée de l'ordre de 20 kO, "consomme" moins qu'un circuit TTL de la famille stadard 74xx qui présente une impédance d'entrée de l'ordre de 2 kO. Tant qu'on est dans le sujet, précisions que la sortance d'un circuit logique est très souvent donnée pour un régime statique, c'est à dire pour un état logique établi et qui ne change pas. En régime dynamique (avec des états logiques qui changent sans arrêt), la sortance peut diminuer. Ce point doit être vérifier avec attention si on veut faire travailler les circuits à grande vitesse.Seuils de basculement

La tension présente sur une entrée de porte logique peut prendre une infinité de valeur entre deux extrêmes, par exemple entre 0 V et +5 V. Les seuils autour desquels le circuit logique considère qu'il a affaire à un état logique bas ou à un état logique haut dépendent du type de circuit logique. Ils diffèrent entre circuits TTL et CMOS, mais ils peuvent aussi différer dans une même famille, selon que les entrées sont standard ou à trigger de Schmitt.- Circuits TTL : un état logique bas est garanti si la tension d'entrée n'excède pas 0,8 V et un état logique haut est garanti si la tension d'entrée est d'au moins 2,0 V.

- Circuits CMOS à entrée standard et sortie bufférisée : seuil unique pour état haut et état bas, 50% tension alim. Un état logique bas est garanti si la tension d'entrée n'excède pas 1,5 V et un état logique haut est garanti si la tension d'entrée est d'au moins 3,5 V (alim 5 V).

- Circuits CMOS à entrée standard et sortie non bufférisée : seuil unique pour état haut et état bas, 50% tension alim. Un état logique bas est garanti si la tension d'entrée n'excède pas 1,0 V et un état logique haut est garanti si la tension d'entrée est d'au moins 4,0 V (toujours pour alim 5 V).

- Circuits CMOS à entrée trigger de Schmitt : tension de seuil typique de 2,9 V pour passage état bas vers état haut et tension de seuil typique de 2,2 V pour passage état haut vers état bas (si alim 5 V).

Tensions de sortie

Il est bien de s'intéresser aux seuils de basculement des entrées des circuits logiques, mais il l'est également de connaître les valeurs de tension de sortie de circuits qui y seront raccordés. Car c'est bien l'ensemble de ces informations qui permettra au final de conclure si oui ou non il y a compatibilité entre les diverses familles. Là encore les valeurs diffèrent entre les différentes familles de circuits logiques (et oui, elles auraient pu ne différer qu'au niveau des entrées, mais ce n'est pas le cas).- Circuits TTL : état bas = 0,4 V maxi et état haut = 2,4 V mini.

- Circuits CMOS à sortie bufférisée : état bas = 0,05 V et état haut = 4,95 V, pour un courant de sortie inférieur à 1 uA !

- Circuits CMOS à sortie non bufférisée :

Impédance de sortie

L'impédance de sortie d'un circuit logique, dont dépendent directement la sortance et l'immunité au bruit, dépend de sa famille.- Circuits TTL : valeur typique comprise entre 8 et 25 ohms à l'état bas

- Circuits CMOS à sortie bufférisée : valeur typique de 250 ohms (avec tension d'alim de 5 V)

- Circuits CMOS à sortie non bufférisée : je ne sais pas mais à mon avis c'est bien supérieur à 250 ohms.

Procédures de test

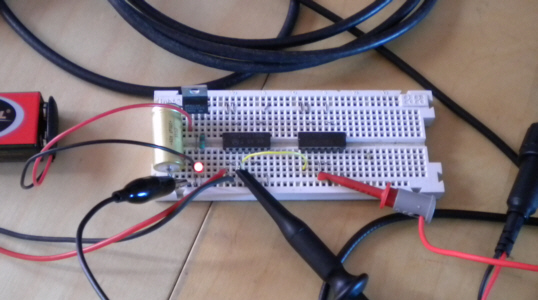

Voilà, nous pouvons maintenant continuer nos petites expériences, avec les conditions de test suivantes :- La tension d'alimentation des circuits TTL et des circuits CMOS sera toujours commune à tous les circuits logiques et de valeur égale à 5 V.

- Les entrées des portes logiques inutilisées sont toutes reliées à la masse, au +5 V ou sur la sortie d'une autre porte dont les entrées ne sont pas laissées en l'air.

- Les circuits sont testés avec des signaux logiques (carrés) d'amplitude 5 V crête à crête et à des fréquences de 200 kHz et 1 MHz (pas la peine d'aller plus loin avec une tension d'alimentation limitée à 5 V et avec une plaque d'expérimentation sans soudure, les constats qu'on pourrait faire ne seraient pas forcement très pertinents).

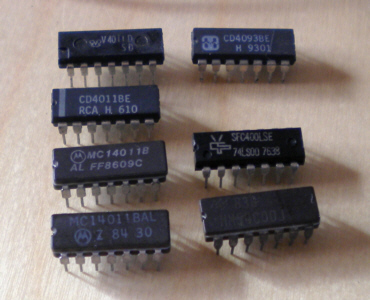

- Sur les schémas qui vont suivre, j'ai appelé "4011" les portes CMOS car j'ai essayé avec des CD4011 et des CD4011BE, et j'ai appelé "7400" les portes TTL en ayant essayé des MM5400 (vieille génération) et des 74LS00 (plus récents et normalement plus performants).

- Des relevés graphique des signaux logiques sont effectués avec un oscilloscope à deux endroits en même temps : en sortie de la première porte (courbe bleue) et en sortie de la seconde (courbe rouge). Cela permet d'une part de voir ce qui se passe au niveau de l'adaptation entre les deux, et de voir d'autre part comment la seconde porte s'en sort avec des signaux éventuellement dégradés. Se référer au nom donné aux graphes pour connaitre les circuits testés et la fréquence du signal test.

Remarque

Dans un premier temps, je comptais relier la sortie d'une porte (TTL ou CMOS) vers une seule autre porte (CMOS ou TTL). Et puis je me suis dit qu'il serait intéressant de voir dès le début ce qui se passait avec une sortie de porte reliée sur quatre autres portes. En théorie cette deuxième façon de faire est plus "méchante" et si donc elle fonctionne on peut dire que ça fonctionne aussi quand on ne relie qu'une seule porte à la sortie de la première. Les schémas de mise en application des tests qui suivent montrent une seule porte reliée sur la sortie de la première, mais côté proto il y en a bien quatre.CMOS vers TTL

Le circuit simple suivant montre une sortie de porte logique CMOS reliée sur les entrées d'une porte logique TTL.

Analyse statique théorique

Si l'entrée de la porte CMOS (In-1) est portée à un potentiel nul (0 V, état logique bas), alors la sortie de cette même porte CMOS (TP1) est à l'état logique haut puisque montée en inverseuse. Dans cette condition, l'entrée TTL peut absorber un courant qui peut atteindre 1,5 mA et faire chuter la tension de sortie de la porte CMOS à une valeur à peine supérieure à 2,5 V. Bien qu'on pourrait considérer cette tension comme un peu limite (on en perdrait tout de même la moitié), tout se passerait bien car l'entrée de la porte TTL voit là et sans ambiguïté un état logique haut puisque pour cela il lui faut au moins 2,0 V. Si maintenant l'entrée de la porte CMOS (In-1) est portée à un potentiel positif de +5 V (état logique haut), alors la sortie de cette même porte CMOS (TP1) est à l'état logique bas. Dans cette condition, le courant d'entrée de la porte TTL est voisin de 0,4 mA et la tension de sortie de la porte CMOS possède une valeur voisine de 0,4 V. Cette valeur, puisque bien inférieure à 0,8 V, est bien considérée comme un état logique bas par la porte TTL.Conclusion : compatibilité assurée. Attention cependant, cette compatibilité risque de souffrir si au lieu de mettre une seule porte TTL vous en mettez un grand nombre en parallèle ! Dans ce cas il vous faudra choisir une famille de circuits TTL qui "consomme" moins (impédance d'entrée plus élevée), comme c'est le cas de la famille TTL LS (74LS00 par exemple) ou HCT (47HCT00 par exemple) par rapport au TTL standard (7400 par exemple).

Tests pratiques

Les graphes suivants montrent que la chute de tension sur l'entre-deux portes est quasiment nulle avec une porte CMOS de type CD4011D ou CD4011BE suivie d'une porte TTL de type MM5400 (version ancienne et compatible du SN7400). Tout au plus pouvons-nous constater de légères différences au niveau des temps de montée et de descente des fronts, CD4011BE plus rapide que le CD4011D.

Et voici ce qui se passe si on remplace le MM5400 par un 74LS00 et qu'on conserve le CMOS CD4011BE.

On constate un très net raidissement des fronts, à tel point qu'on a maintenant droit à de superbes suroscillations dont on se passerait bien. Ces suroscillations apparaissent aussi et avec la même amplitude à une fréquence de 1 kHz et avec un découplage d'alimentation local additionnel (10 uF et 10 nF aux bornes d'alimentation du circuit TTL). En poussant la fréquence du signal test à 2 MHz, on se rend compte sans trop de surprise que le circuit ne suit plus très bien et que le signal de sortie final n'est plus du tout exploitable.

TTL vers CMOS

Le circuit simple suivant montre une sortie de porte logique TTL reliée sur les entrées d'une porte logique CMOS.

Analyse statique théorique

Si l'entrée de la porte TTL (In-2) est portée à un potentiel nul (0 V, état logique bas), alors la sortie de cette même porte TTL (TP2) est à l'état logique haut puisque montée en inverseuse. Dans cette condition, l'entrée CMOS voit une tension qui peut être supérieure à 2,5 V, mais qui peut aussi être aussi faible que 2,4 V puisque cette tension est encore "valide" pour représenter un état haut en logique TTL. Si maintenant l'entrée de la porte TTL (In-2) est portée à un potentiel positif de +5 V (état logique haut), alors la sortie de cette même porte TTL (TP2) est à l'état logique bas. Dans cette condition, l'entrée CMOS voit une tension qui est sans problème considérée comme étant un état logique bas.A cause du premier cas de figure, il y a incompatibilité et on ne peut pas sérieusement accépter un tel montage. Une solution simple consiste à ajouter une résistance de tirage vers le +5 V (pullup) afin de remonter le potentiel de sortie de la porte TTL quand cette dernière est à l'état haut.

Cette résistance additionnelle aura une incidence négligeable quand la sortie de la porte TTL sera à l'état logique bas.

Tests pratiques

Tests réalisés avec un TTL 74LS00 suivi d'un CMOS 4011BE, avec et sans résistance de rappel au +5 V entre les deux. Pour commencer, sans résistance de rappel :

On constate bien une chute de l'amplitude du signal rectangulaire en sortie de la première porte logique, comme prévue en théorie. Elle est cependant moindre que le pire cas auquel on pouvait s'attendre, malgré un câblage de une porte vers quatre autres. L'ajout d'une résistance de rappel de 2,7 kO entre la sortie de la première porte et le +5 V apporte effectivement une nette amélioration dans ce sens, à savoir rétablissement du signal à une amplitude de 5 V crête à crête.

Nettement mieux, mais pas suffisant pour grimper à 2 MHz comme en atteste la dernière copie d'écran de l'oscilloscope. Mais rappelez-vous : technologie CMOS alimentée et 5 V et montage sur plaque d'expérimentation...