Electronique

>

Réalisations

> Interfaces

> Interface port parallèle (LPT) 002

Dernière mise à jour : 01/08/2010Présentation

Cette interface a été spécifiquement développée pour le pilotage d'un port parallèle de PC via mon logiciel ProgSeq, et permet de disposer de 32 sorties individuelles. Il s'agit d'une version étendue de l'interface port parallèle 001 qui elle ne possède que 8 sorties. Moyennant l'ajout de quelques circuits intégrés, le nombre de sorties individuelles peut monter à 120.Schéma de l'interface 8 bits / 32 voies

Le schéma suivant représente la partie "décodage"

qui permet de travailler sur quatre blocs de huit lignes de

données à partir de l'unique bus de données huit

bits du port parallèle (D0 à D7) et de quatre bits de

contrôle

issus du même port (Strobe, Autofeed, Init et Select).

Avant toute chose...

Vous êtes plusieurs à m'avoir écrit pour me demander ce que représentait la ligne bleue sur le schéma. Cette ligne est ce qu'on appelle une ligne de bus, détails à la page Schémas du site - Conventions.Descriptif général

Le circuit peut paraître complexe, mais le principe est très simple. On dispose de huit lignes de données, et on veut que ces huit lignes véhiculent l'état de 32 sorties. Faire ça en une seule fois est tout bonnement impossible, c'est comme vouloir faire passer cote à cote 6 voitures sur une route à deux voies. Mais faire ça en plusieurs fois est possible, c'est ce qu'on appelle le multiplexage temporel : les voitures ne sont pas cote à cote, mais se suivent. Le principe consiste à travailler avec un premier groupe de huit sorties (sorties 1 à 8), puis une fois que ce qui devait être fait est fait avec ce groupe (par exemple activer la sortie 3), à passer au second groupe de huit sorties (sorties 9 à 16), faire ce qu'il faut avec ce groupe, et ainsi de suite. Une fois le quatrième groupe traité (sorties 25 à 32), on s'occupe à nouveau du premier groupe. Bien entendu, si on veut avoir une impression d'instantanéité, il ne faut pas trop s'attarder entre le traitement du premier et du dernier groupe. Dans le cas présent, le traitement de toutes les sorties prend moins d'une milliseconde, ça ne se voit pas à l'oeil nu. Voyons maintenant comment cela peut fonctionner.Chaque groupe de 8 sorties peut recevoir les informations transmises par le bus de données du port parallèle (D0 à D7), au travers d'une petite "porte à mémoire". Cette "porte à mémoire" est un composant qui possède un certain nombre d'entrées (ici huit, quel hasard), des sorties (là aussi huit), et une petite patte de commande magique qui va ouvrir ou fermer la porte. Quand cette patte de commande est à l'état logique haut (+5V), les sorties sont au même état logique que leur entrées respectives (la sortie Q1 est au même état logique que l'entrée I1). Quand la patte de commande passe à l'état logique bas (0V), les sorties restent dans l'état où elles étaient au moment du basculement, et si à cet instant les entrées changent d'état, les sorties n'en laissent rien paraître, elles font la sourde oreille et ne changent donc pas d'état. Voilà, il suffit donc de brancher en parallèle les entrées des "portes à mémoire" de chaque groupe, mais à un instant donné, n'ouvrir qu'une seule porte à la fois. Une routine toute simple telle que celle qui suit, accomplit la tache désirée avec brio :

01 - Envoi de l'état des sorties 1 à 8 sur le bus de données D0 à D7 du port parallèle.

02 - Ouverture puis fermeture de la "porte à mémoire" N°1 (les sorties O1 à O8 prennent l'état des données D0 à D7)

03 - Envoi de l'état des sorties 9 à 16 sur le bus de données D0 à D7 du port parallèle.

04 - Ouverture puis fermeture de la "porte à mémoire" N°2 (les sorties O9 à O16 prennent l'état des données D0 à D7)

05 - Envoi de l'état des sorties 17 à 24 sur le bus de données D0 à D7 du port parallèle.

06 - Ouverture puis fermeture de la "porte à mémoire" N°3 (les sorties O17 à O24 prennent l'état des données D0 à D7)

07 - Envoi de l'état des sorties 25 à 32 sur le bus de données D0 à D7 du port parallèle.

08 - Ouverture puis fermeture de la "porte à mémoire" N°4 (les sorties O25 à O32 prennent l'état des données D0 à D7)

09 - Envoi de l'état des sorties 1 à 8 sur le bus de données D0 à D7 du port parallèle.

10 - Ouverture puis fermeture de la "porte à mémoire" N°1 (les sorties O1 à O8 prennent l'état des données D0 à D7)

etc.

Les "portes à mémoire" que j'ai décidé d'utiliser sont des 74HCT373, et portent le doux nom de "octuple verrou transparent" (octal transparent latch). Ca vous aide beaucoup si je vous dit que dans ce circuit il y a des bascules (flip-flop) ? La broche de commande s'appelle LE, comme Latch Enable (activation verrou). Vous pouvez voir sur le schéma que la borne LE de chaque circuit est controlée par une des lignes de contrôle du port parallèle, via des liaisons appelées Sel1 à Sel4. Les circuits 74HCT373 possèdent en outre une broche qui permet d'isoler les sorties (de les placer à l'état haute impédance), mais comme nous n'avons pas besoin de cette fonction, cette broche (OE barre, OE comme Output Enable) sera toujours au même état logique, ici à l'état bas pour des sorties toujours actives.

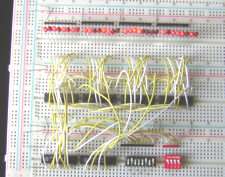

Proto de l'interface 32 voies

Partie décodage seule, sans partie puissance. Réalisé sur plaque d'expérimentation sans soudure.

Les leds remplacent ici les optocoupleurs qui seront par la suite

réellement mis en oeuvre (voir paragraphe Section puissance).

Tests effectués ici avec microswitches : 8 pour les données D0 à D7, et 4 pour les quatre groupes. Test en grandeur nature réalisé également avec un PC portable doté d'un port parallèle, que j'ai emprunté car le mien ne dispose pas d'un tel port. Fonctionnement OK là aussi avec mon soft ProgSeq.

Plus de 32 voies de sorties ?

32 sorties vous semblent insuffisantes ? Moyennant l'ajout d'un circuit intégré décodeur BCD / Décimal de type 74HCT4028 (ou CD4028) et de quatre verrous octuples, il est possible de porter le nombre de sorties de 32 (4 groupes de 8 sorties) à 64 (8 groupes de 8 sorties), très facilement. C'est ce que montre le schéma suivant.

Et en remplaçant le décodeur BCD / Décimal 4028 (10 sorties) par un décodeur BCD / Décimal de type 4514 (16 sorties), on peut porter le nombre de sorties à 120 (15 groupes de 8 sorties). Pour un nombre de groupes supérieur à quatre, l'état logique des quatre lignes de contrôle du port parallèle doit évidement être élaboré selon un code BCD (ou binaire) et non décimal, pour qu'au lieu d'avoir 4 possibilités (une ligne de contrôle active à la fois), on en ait 16 (toutes combinaisons possibles avec 4 bits). Pourquoi je parle de 15 groupes alors que l'on dispose de 16 sorties avec le décodeur BCD / Décimal 4514 ? Par ce que je ne compte pas la première sortie du décodeur, qui correspond à la combinaison binaire "0000". Sortie que l'on pourrait utiliser mais pas avec la même souplesse.

Section puissance

Le schéma suivant représente un bloc de puissance 5 V / 230 V avec isolation par optotriacs, pour un ensemble de huit sorties, et doit être réalisée en quatre exemplaires pour bénéficier de 32 sorties (ou en deux exemplaires seulement si 16 voies vous suffisent). Cette interface est une copie multipliée de celle "unitaire" décrite à la page Interface de puissance 5V / 230V 001.

Je ne sais pas ce qui m'a prit, mais ce schéma est identique à celui de l'interface LPT 001 8 voies. Allez donc y jeter un oeil si le dessin du CI vous intéresse.

Interface LPT 001 (ou 002c) sans transistor additionnel

Si la partie commande (sortie port imprimante ou autres sorties TTL ou CMOS) ne délivre pas un courant de commande suffisant pour allumer franchement les leds (externes et intégrées dans les optotriacs) de l'interface de puissance, vous pouvez ajouter un transistor supplémentaire sur chaque entrée, qui joue alors le rôle d'amplificateur de courant. Voir exemple en page Interface LPT 003.

Interface LPT 003 avec transistors additionnels ou ULN2803

Il n'est pas trop de rappeler que ce montage comporte une partie reliée au secteur 230 V, et que les précautions d'usage s'imposent. Pour les supports fusibles, préférez les modèles isolés pour circuit imprimé, ou les modèles à fixer sur chassis. Evitez les modèles non isolés pour circuit imprimé, plus économique mais plus dangeureux.

Correctifs et remarques

27/01/2008- Correction sur schéma interface 8 bits / 32 voies : la borne 15 de J2 n'était pas reliée à la masse du connecteur port parallèle J1 (bornes 18 à 25). Le schéma actuel est corrigé. Merci à Sébastien C., qui a réalisé cette interface avec succès, de m'avoir signalé cet oubli.